ALU (Arithmetic and Logic Unit):

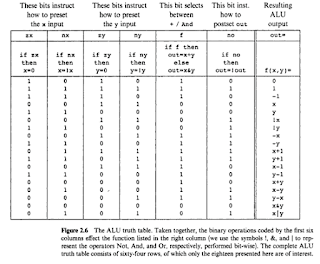

The basic building block for a computer is ALU which can perform the basic Arithmetic and logical operations. The Chip creation using the HDL from the basic gates(AND,NOT,MUX,ADDER..etc) gives you the in site knowledge and interest for binary number operations. The below HDL ALU chip can perform 18 operations, potentially which can compute 64.

Follow the course The Elements of Computing Systems

CHIP ALU {

IN // 16-bit inputs:

x[16], y[16],

// Control bits:

zx, // Zero the x input

nx, // Negate the x input

zy, // Zero the y input

ny, // Negate the y input

f, // Function code: 1 for add, 0 for and

no; // Negate the out output

OUT // 16-bit output

out[16],

// ALU output flags

zr, // 1 if out=0, 0 otherwise

ng; // 1 if out<0, 0 otherwise

PARTS:

Mux16(a[0..15]=x[0..15], b[0..15]=false, sel=zx, out[0..15]=x1);

Mux16(a[0..15]=y[0..15], b[0..15]=false, sel=zy, out[0..15]=y1);

Not16(in[0..15]=x1, out[0..15]=notx1);

Not16(in[0..15]=y1, out[0..15]=noty1);

Mux16(a[0..15]=x1, b[0..15]=notx1, sel=nx, out[0..15]=x2);

Mux16(a[0..15]=y1, b[0..15]=noty1, sel=ny, out=y2);

And16(a[0..15]=x2, b[0..15]=y2, out=Andxy);

Add16(a[0..15]=x2, b[0..15]=y2, out=Addxy);

Mux16(a[0..15]=Andxy, b[0..15]=Addxy, sel=f, out=x3);

Not16(in[0..15]=x3, out=notx3);

Mux16(a[0..15]=x3, b[0..15]=notx3, sel=no, out[0]=ou1,out[1]=ou2,out[2]=ou3,out[3]=ou4,out[4]=ou5,out[5]=ou6,out[6]=ou7,out[7]=ou8,out[8]=ou9,out[9]=ou10,out[10]=ou11,out[11]=ou12,out[12]=ou13,out[13]=ou14,out[14]=ou15,out[15]=ou16);

Or(a=ou1, b=ou2,out= out1);

Or(a=ou2,b= out1,out= out2);

Or(a=ou3,b= out2,out= out3);

Or(a=ou4,b= out3,out= out4);

Or(a=ou5,b= out4,out= out5);

Or(a=ou6,b= out5,out= out6);

Or(a=ou7,b= out6,out= out7);

Or(a=ou8,b= out7,out= out8);

Or(a=ou9,b= out8,out= out9);

Or(a=ou10,b= out9,out= out10);

Or(a=ou11,b= out10,out= out11);

Or(a=ou12,b= out11,out= out12);

Or(a=ou13,b= out12,out= out13);

Or(a=ou14,b= out13,out= out14);

Or(a=ou15,b= out14,out= out15);

Or(a=ou16,b= out15,out= notzr);

Not(in=notzr,out=zr);

And(a=ou16,b=true,out=ng);

And(a=ou1,b=true,out=out[0]);

And(a=ou2,b=true,out=out[1]);

And(a=ou3,b=true,out=out[2]);

And(a=ou4,b=true,out=out[3]);

And(a=ou5,b=true,out=out[4]);

And(a=ou6,b=true,out=out[5]);

And(a=ou7,b=true,out=out[6]);

And(a=ou8,b=true,out=out[7]);

And(a=ou9,b=true,out=out[8]);

And(a=ou10,b=true,out=out[9]);

And(a=ou11,b=true,out=out[10]);

And(a=ou12,b=true,out=out[11]);

And(a=ou13,b=true,out=out[12]);

And(a=ou14,b=true,out=out[13]);

And(a=ou15,b=true,out=out[14]);

And(a=ou16,b=true,out=out[15]);

}

No comments:

Post a Comment